## (19) United States

### (12) Patent Application Publication (10) Pub. No.: US 2004/0164684 A1 Inukai et al.

(43) Pub. Date:

Aug. 26, 2004

### (54) EL DISPLAY DEVICE AND ELECTRONIC **APPARATUS**

(75) Inventors: Kazutaka Inukai, Kanagawa (JP); Jun Koyama, Kanagawa (JP)

> Correspondence Address: Edward D. Manzo Cook, Alex, McFarron, Manzo, Cummings & Mehler, Ltd. 200 West Adams St., Ste. 2850 Chicago, IL 60606 (US)

(73) Assignee: Semiconductor Energy Laboratory Co., Ltd.

(21) Appl. No.: 10/745,153

(22) Filed: Dec. 23, 2003

### Related U.S. Application Data

Continuation of application No. 09/715,528, filed on Nov. 17, 2000, now Pat. No. 6,680,577.

#### (30)Foreign Application Priority Data

| Nov. 29, 1999 | (JP) | 11-338845   |

|---------------|------|-------------|

| Oct. 2, 2000  | (JP) | 2000-302979 |

### **Publication Classification**

| (51) | Int. Cl. <sup>7</sup> |  |

|------|-----------------------|--|

| (52) | U.S. Cl.              |  |

#### (57)ABSTRACT

An EL display device capable of clear, multi-gradation color display, and an electronic device having the EL display device, are provided. Gradation display is performed in accordance with a time division driver method which controls by the amount of time an EL element formed in a pixel emits light, and the amount of time it does not emit light. Influence due to dispersion in the characteristics of electric current TFTs is prevented.

FIG. IA

FIG. IB

202 54 **EMISSION DIRECTION** <u>201</u> 47 204 20

FIG. 6

### SOURCE DRIVER CIRCUIT

FIG. 7

MI,M2;L=I2W,W=35 X2 [μm] CI;S=0.I4 X 0.I4 [mmi] (GTO-AI間) RI;L=800,W=I0 [μm] (AI), R2;L=59I, W=3 [μm] (LDDSi)

FIG. 13

FIG.2I

614

1205

## FIG.26

# FIG.27A

# FIG.27B

FIG. 28A

FIG. 28B

FIG. 29

FIG. 30A

FIG. 30B

FIG. 30C

FIG. 30D

FIG. 30E

FIG. 3IA FIG. 3IB FIG. 3IC

FIG. 32

FIG. 33

## EL DISPLAY DEVICE AND ELECTRONIC APPARATUS

### BACKGROUND OF THE INVENTION

[0001] 1. Field of the Invention

[0002] The present invention relates to an EL (electroluminescence) display device formed by a semiconductor element (an element using a semiconductor thin film) made on a substrate, and to an electronic apparatus having the EL display device as a display (display portion).

[0003] 2. Description of the Related Art

[0004] Techniques of forming a TFT on a substrate have been greatly advancing in recent years, and development of applications to an active matrix type display device have been progressing. In particular, a TFT using a polysilicon film has a higher electric field effect mobility (also referred to as mobility) than a TFT which uses a conventional amorphous silicon film, and high speed operation is therefore possible.

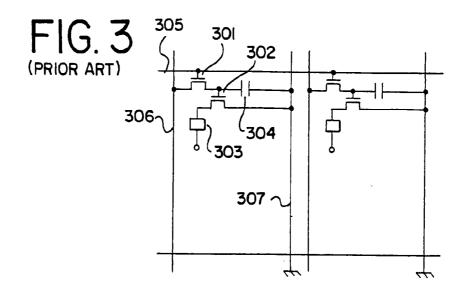

[0005] Shown in FIG. 3 is a general pixel structure of an active matrix type EL display device. Reference numeral 301 in FIG. 3 denotes a TFT which functions as a switching element (hereafter referred to as a switching TFT), reference numeral 302 denotes a TFT which functions as an element (hereafter referred to as an electric current control element) for controlling electric current provided to an EL element 303, and 304 denotes a capacitor (storage capacitor). The switching TFT 301 is connected to a gate wiring 305 and to a source wiring (data wiring) 306. A drain of the electric current control TFT 302 is connected to the EL element 303, and a source of the electric current control TFT 302 is connected to an electric current supply wiring 307.

[0006] A gate of the switching TFT 301 opens when the gate wiring 305 is selected, a data signal of the source wiring 306 is stored in the capacitor 304, and a gate of the electric current control TFT 302 opens. After the gate of the switching TFT 301 closes, the gate of the electric current control TFT 302 remains open in accordance with the electric charges stored in the capacitor 304, and the EL element 303 emits light during that period. The amount of light emitted by the EL element 303 is changed by the amount of electric current

[0007] In other words, the amount of electric current flowing in the electric current control TFT 302 is controlled by the data signal input from the source wiring 306 in an analog drive gradation display, and the amount of light emitted by the EL element thereby changes.

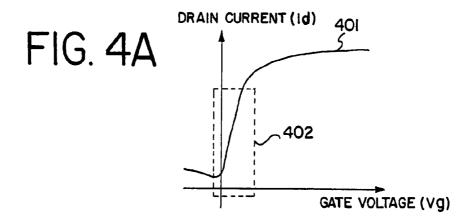

[0008] FIG. 4A is a graph showing the transistor characteristics of the electric current control TFT 302, and reference numeral 401 denotes an Id-Vg characteristic (also referred to as an Id-Vg curve). Id is a drain current, and Vg is a gate voltage here. The amount of electric current flowing with respect to an arbitrary gate voltage can be found with this graph.

[0009] A region of the Id-Vg characteristic shown by a dotted line 402 is normally used in driving the EL elements. An enlargement of the region enclosed by the region 402 is shown in FIG. 4B.

[0010] The shaded region in FIG. 4B is referred to as a subthreshold region. In practice, this indicates a region

having a gate voltage in the neighborhood of the threshold voltage (Vth) or below, and the drain current changes exponentially with respect to changes in the gate voltage within this region. Electric current control is performed in accordance with the gate voltage by using this region.

[0011] The data signal input to the pixel when the switching TFT 301 in FIG. 3 is open is first stored in the capacitor 304, and then the signal becomes the gate voltage of the electric current control TFT 302, as is. The drain current is determined at this time by a one to one correspondence with respect to the gate voltage, in accordance with the Id-Vg characteristic shown in FIG. 4A. Namely, a predetermined electric current flows in the EL element 303 in correspondence with the data signal, and the EL element 303 emits light with the amount of light corresponding to the amount of current flow.

[0012] The amount of light emitted by the EL element is thus controlled by the input signal, and gradation display is performed by controlling the amount of light emitted. This method is referred to as analog gradation, and gradation display is performed by changing the amplitude of the signal.

[0013] However, the above analog gradation method has a disadvantage of being extremely weak with respect to dispersions in the TFT characteristics. For example, suppose that the Id-Vg characteristic is a switching TFT and differs from that of a switching TFT of an adjacent pixel displaying the same gradation (a case of an overall positive of negative shift).

[0014] In this case the drain current of each switching TFT differs on the order of the dispersion, and the gate voltages applied to the current control TFTs of each pixel therefore also differ. In other words, the electric current flowing differs for each of the EL elements, and as a result, the amount of light emitted also differs, and the same gradation display cannot be performed.

[0015] Further, even supposing that equal gate voltages are applied to the electric current control TFTs of each pixel, the same drain current cannot be output if there are variations in the Id-Vg characteristics of the electric current control TFTs. In addition, even if equal gate voltages are applied, the amount of electric current output differs greatly if even small deviations exist in the Id-Vg characteristics when using a region in which the drain current changes exponentially with respect to changes in the gate voltage, as is clear from FIG. 4A. The amount of light emitted by adjacent pixels will differ greatly as a result.

[0016] In practice, there is a multiplier effect between dispersions in both the switching TFTs and the electric current control TFTs, and this makes achieving the conditions more difficult. Thus the analog gradation method is extremely sensitive with respect to variations in the TFT characteristics, and this becomes an obstacle to multiple colorization of a conventional active matrix EL display device.

### SUMMARY OF THE INVENTION

[0017] In consideration of the above problems, an object of the present invention is to provide an active matrix type EL display device capable of sharp, multi-gradation color display. In addition, an object of the present invention is to

provide a high performance electrical apparatus furnished as a display portion of this type of active matrix EL display device.

[0018] The applicant of the present invention considers that in order to make a pixel structure which is not readily influenced by dispersions in TFT characteristics, a digital driver gradation method, in which an electric current control TFT is used as a simple electric current supply switching element, is better than a conventional analog driver gradation method of controlling the amount of light emitted by an EL element in accordance with electric current control.

[0019] It is considered that a time division method of gradation display (hereafter referred to as time division gradation) will be performed by a digital driver in the active matrix type EL display device.

[0020] In addition, a panel display can be made higher speed by dividing video lines and inputting a plurality of data at one time when inputting a video signal into a source driver circuit. Note that the video signal referred to here is a data signal input into the source driver circuit throughout this specification.

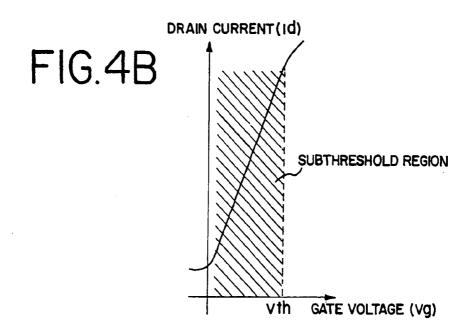

[0021] FIGS. 5A to 5F show the overall driver timing of the write-in period and the display period when performing time division gradation display. A case of performing 64 gradation display in accordance with a 6 bit digital driver method is explained here. Note that the write-in period is the time required for a signal to be written into all pixels structuring one frame, and that the display period is the period in which the pixels perform display of the write-in signal.

[0022] An EL driver power supply is cut (all pixels turn off) during the write-in period, and the EL elements within the pixels are in a state of no applied voltage. Further, the EL driver power supply is input during the display period, placing the EL elements within the pixels in a state of having an applied voltage. At this point the pixels turn on when the data signal for turning on the pixels is input.

[0023] A period in which an image is completely displayed in an image region is referred to as one frame period. The oscillation frequency of a normal EL display is 60 Hz, and 60 frames exist during one second, as shown in FIG. 5A. For example, when performing 6 bit digital gradation display (64 gradations) in a fourth frame, if one frame is divided into 16 partitions and the ratio of the write-in period to the display period is determined as 6:10, then writing in can be performed 6 times (≈6.24 msec) during the write-in period, as shown in FIG. 5B. Note that the six write-ins 1 to 6 are performed in order from 1 to 6. Further, the display periods corresponding to the write-in periods (from write-in 1 to write-in 6) are set as displays 1 to 6, respectively.

[0024] Furthermore, the display periods are set so that display 1: display 2: display 3: display 4: display 5: display 6=1:  $\frac{1}{2}$ :  $\frac{1}$

[0025] FIG. 5C shows a state in which each display period has the above stated ratios with respect to the write-ins when performing 6 write-ins (write-in 1 to write-in 6) during one frame. The values shown in the lower portion of FIG. 5C show the relationship between the lengths of the write-in periods and the display periods.

[0026] Specifically, the display period (display 1) in the write-in 1 shows a value of 320 when the write-in period is 63. In addition, the display 2 has a display period of 160, the display 3 has a display period of 80, the display 4 has a display period of 40, the display 5 has a display period of 20, and the display 6 has a display period of 10 with respect to each of the write-in periods having a value of 63.

[0027] One write-in period (write-in) and one display period (display) together are referred to as one field. Namely, six fields exist in FIG. 5C, all having constant write-in periods and differing display periods. In order to complete one frame here, the first field displayed at the beginning is referred to as a field 1 (F1), and the fields displayed subsequently below are referred to as fields 2 to 6 (F2 to F6), in order.

[0028] Note that the order of appearance of the fields 1 to 6 may be arbitrary. By combining the display periods, a desired gradation display, from among the 64 gradations, can be performed.

[0029] Further, in practice the timing is a combination of the six dispersed fields having different display periods, as shown in FIG. 5D.

[0030] If predetermined pixels are turned on during the period of the display 1 in FIG. 5D, then the write-in 5 is entered and after the data signal is input to all of the pixels, the display 5 is entered. Next, the display 4 is entered after the data signal is input to all of the pixels in the write-in 4. Predetermined pixels are also similarly turned on by the respective fields in the write-in 2, the write-in 3, and the write-in 6.

[0031] FIG. 5E shows the period during which the data, with which a certain gate line is selected by the data signal input from a gate circuit in the field 5 from among the six fields shown in FIG. 5D, is written (the write-in S). FIG. 5E also shows the display period (the display S) in which the signal from a source line input from a source line to the selected gate line and the pixels perform display.

[0032] FIGS. 5A to 5E are based on a VGA (640×480) panel display, and therefore there are 480 gate wirings and in addition, a period for selecting all of the gate lines, including a certain number of dummies, is a write-in period of FIG. 5E.

[0033] The signal input from the source lines in the write-in period is referred to as dot data. The dot data input from a source driver circuit during one gate selection period is sampled during a period shown in FIG. 5F. This shows the gate data selected during the write-in period being written in, at the same time as showing the signal input from the source lines being written in. Note that the period for the data to be sampled at one time is 40 nsec.

[0034] Note also that the dot data input from the source driver circuit is input at the same time at 16 bits per 40 nsec as shown in FIG. 5F.

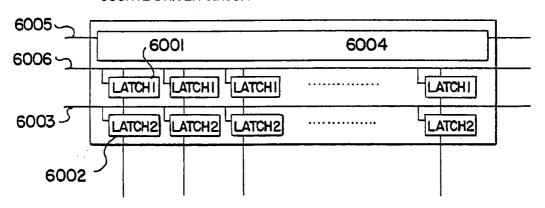

[0035] In addition, the dot data selected in one gate selection period is stored in a latch 1 (6001) within the source driver circuit shown in FIG. 6 until all of the data sampling is completed. After all sampling is finished, latch data is input from a latch line 6003, and all of the data is moved at once to a latch 2 (6002). Note that a shift register

**6004** selects a video signal input from a video line **6006** in accordance with a clock pulse from a clock line **6005**.

[0036] In addition to the sampling period, a line data latch period formed in FIG. 5F is a period in which a latch signal is input when moving the data from the latch 1 (6001) to the latch 2 (6002), and in which the data is moved.

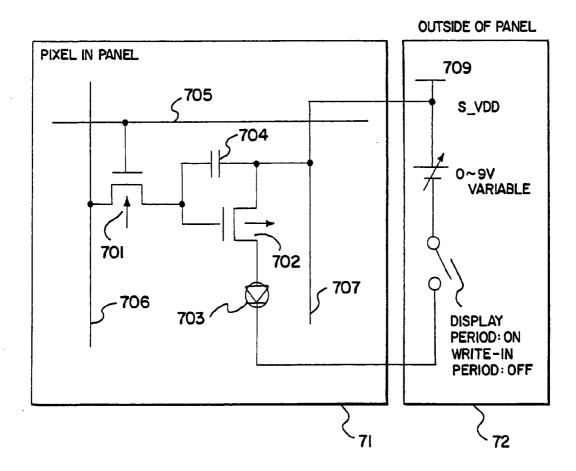

[0037] A pixel structure of an active matrix type EL display device of the present invention is shown in FIG. 7. Reference numeral 701 in FIG. 7 denotes a TFT which functions as a switching element (hereafter referred to as a switching TFT or a pixel switch TFT), reference numeral 702 denotes a TFT (hereafter referred to as an electric current control TFT or an EL driver TFT) which functions as an element (electric current control element) for controlling the electric current supplied to an EL element 703, and reference numeral 704 denotes a capacitor (also referred to as a storage capacitor or a supplementary capacitor). The switching TFT 701 is connected to a gate line 705 and a source line (data line) 706. Further, a drain of the electric current control TFT 702 is connected to the EL element 703, and a source of the electric current control TFT 702 is connected to an electric current supply line (also referred to as an EL driver power supply line) 707.

[0038] A gate of the switching TFT 701 opens when the gate line 705 is selected, the data signal from the source line 706 is stored in capacitor 704, and a gate of the electric current control TFT 702 opens. Then, after the gate of the switching TFT 701 closes, the gate of the electric current control TFT 702 remains open in accordance with the electric charge stored in the capacitor 704, and the EL element 703 emits light during that time. The amount of light emitted by the EL element 703 changes by the amount of electric current flowing.

[0039] In other words, the gate of the electric current control TFT 702 opens or closes in accordance with the data signal input from the source line 706 in the digital drive gradation display, and if the EL driver power supply is on, electric current flows and the EL element emits light.

[0040] The function of the electric current control TFT of the pixel is to control whether or not the corresponding pixel is turned on (display) or is turned off (non-display) during the display period. The switching between the display period and the write-in period is performed by a power source external to the right panel, through an FPC terminal.

[0041] Further, an electric power supply attached externally to the panel (reference numeral 709 in FIG. 7) achieves a switching function for switching between the write-in period and the display period. In the write-in period the electric power supply is in an off state (a state in which there is no applied voltage), and the data signal is input to each of the pixels.

[0042] After the data in input to all of the pixels and the write-in period is complete, the electric power supply (reference numeral 709 in FIG. 7) in turned on and display is performed all at once. This period becomes the display period. The period in which the EL elements emit light and the pixels are turned on is any of the periods from the display 1 to the display 6 from among the six fields.

[0043] After the six fields have appeared, one frame becomes complete. The gradation of a pixel is controlled by

adding up the display periods at this point. For example, when the display 1 and the display 2 are selected, a brightness of 76% can be expressed out of a full brightness of 100%, and when the display 3 and the display 5 are selected, a brightness of 16% can be expressed.

[0044] Note that although a case of 64 gradations is explained above, it is also possible to perform other gradation displays.

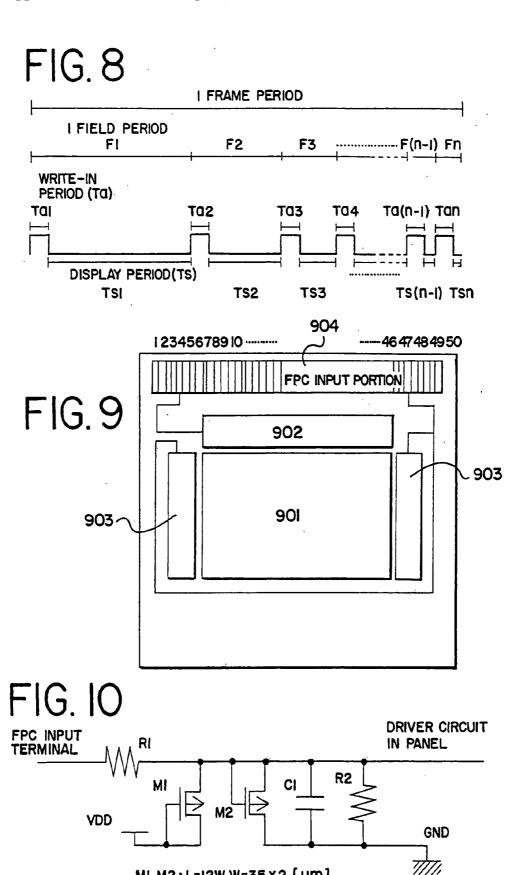

[0045] Assuming that N bit (where N is an integer greater than or equal to 2) gradation display is performed (2<sup>n</sup> gradations), then first one frame is divided into N fields (F1, F2, F3, . . . , F(n-1), F(n)) corresponding to the N bit gradations. The number of divisions of one frame increases with increasing gradations, and the driver circuit must by driven at a high frequency.

[0046] In addition, each of the N fields is separated into write-in periods (Ta) and display periods (Ts).

**[0047]** The display periods (note that display periods corresponding to F1, F2, F3, ..., F(n-1), F(n) are expressed as Ts1, Ts2, Ts3, ..., Ts(n-1), Ts(n), respectively) of the N fields are processed so as to become Ts1: Ts2: Ts3: ...: Ts(n-1):  $Ts(n)=2^0$ :  $2^{-1}$ :  $2^{-2}$ : ...:  $2^{-(n-2)}$ :  $2^{-(n-1)}$ .

[0048] In this state, pixels are selected in order in one arbitrary field (strictly speaking, the switching TFT of each pixel is selected), and the predetermined gate voltage (corresponding to the data signal) is applied to the gate electrodes of the electric current controlling TFTs. The EL elements of pixels to which a data signal, which makes the electric current control TFTs have a continuity state, is input to turn on the pixels for the display periods apportioned to those fields when the electric power supply is input after the write-in period is complete.

[0049] This operation is repeated in all the N fields, and gradation of each pixel is controlled in one frame by adding the display periods. Therefore in focusing on one arbitrary pixel, the gradation of one pixel can be controlled on the basis of for how long a period the pixel was lighted in each field (how many display periods have passed).

[0050] Thus the most important aspect of the preset invention is that the digital driver time dividing gradation method is used in the active matrix type EL display device. It becomes possible to perform gradation display without any influence from the TFT characteristics, a problem in analog driver gradation display, by using this time division gradation driver.

### BRIEF DESCRIPTION OF THE DRAWINGS

[0051] In the accompanying drawings:

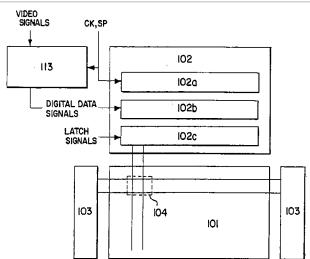

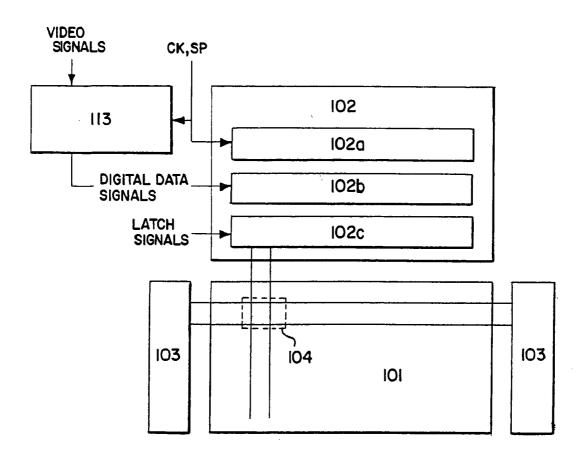

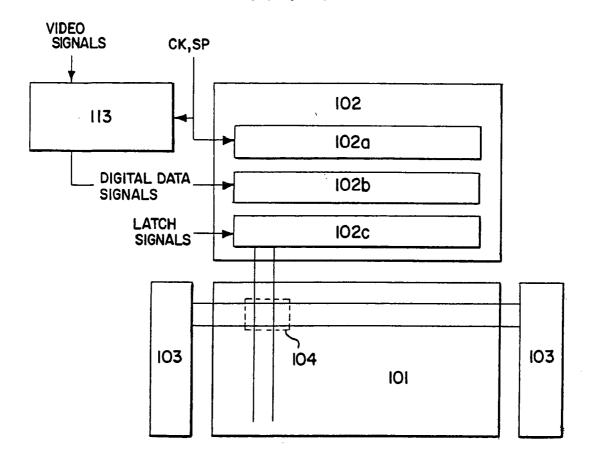

[0052] FIGS. 1A and 1B are diagrams showing the structure of an EL display device;

[0053] FIG. 2 is a diagram showing a cross sectional structure of an EL display device;

[0054] FIG. 3 is a diagram showing the structure of a pixel portion in a conventional EL display device;

[0055] FIGS. 4A and 4B are diagrams for explaining the TFT characteristics utilized by an analog gradation method;

[0056] FIGS. 5A to 5F are diagrams for explaining an operating mode of a time division gradation method;

[0057] FIG. 6 is a diagram showing a source driver circuit of an EL display device;

[0058] FIG. 7 is a diagram showing a pixel structure of a pixel portion of an EL display device;

[0059] FIG. 8 is a diagram for explaining an operating mode of a time division gradation method;

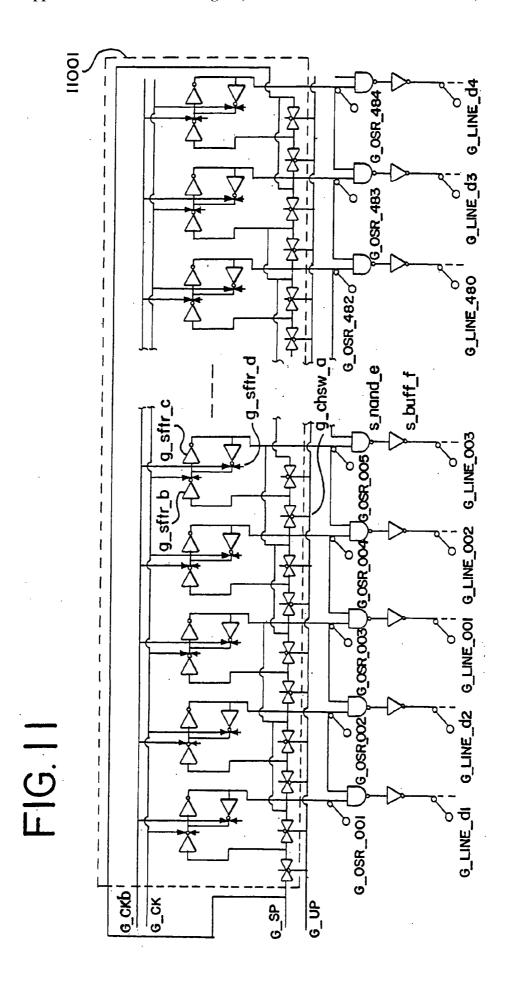

[0060] FIG. 9 is a top view of a complete EL display device panel;

[0061] FIG. 10 is a protecting circuit of an FPC input portion;

[0062] FIG. 11 is a diagram showing a gate driver circuit of an EL display device;

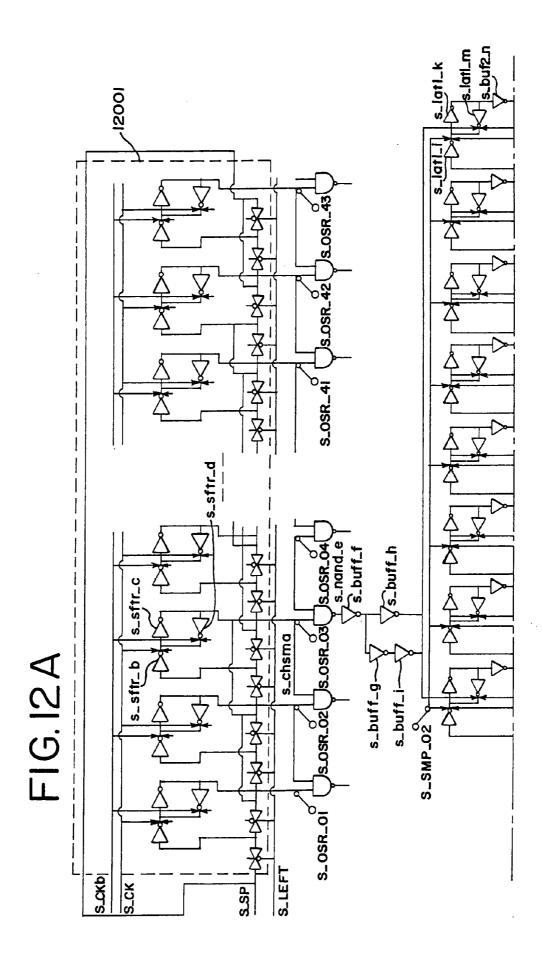

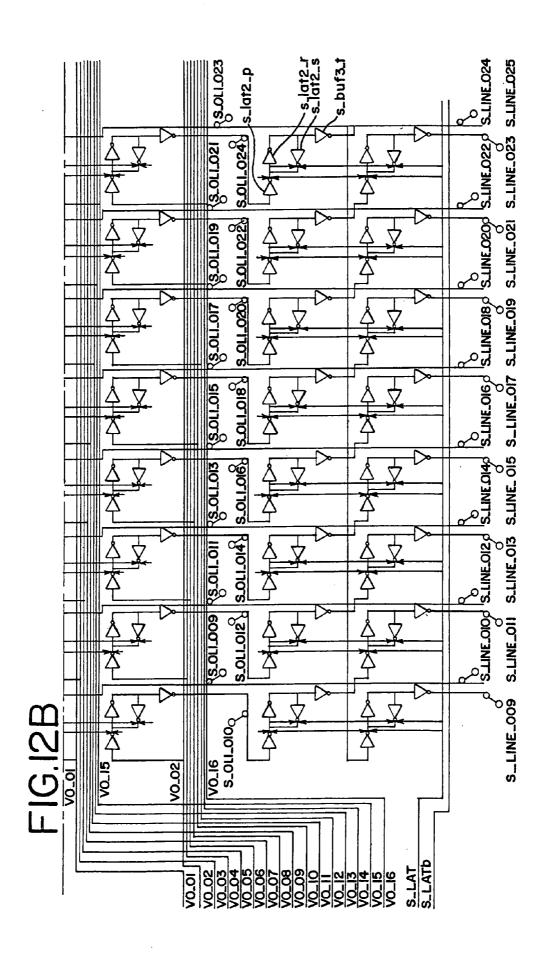

[0063] FIG. 12 is a diagram showing a source driver circuit of an EL display device;

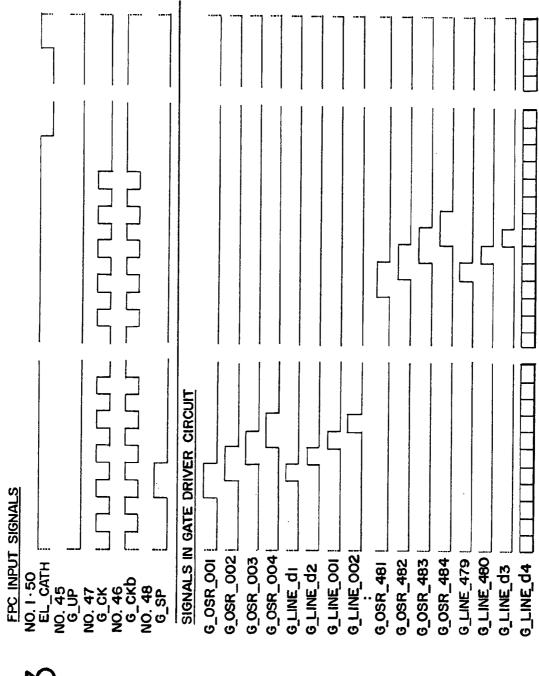

[0064] FIG. 13 is a timing diagram of an input signal from a source driver circuit side of an EL display device;

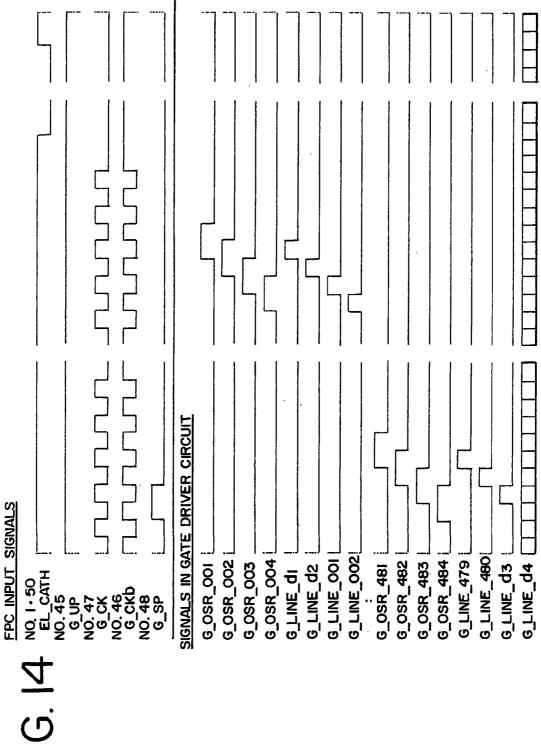

[0065] FIG. 14 is a timing diagram of an input signal from a source driver circuit side of an EL display device;

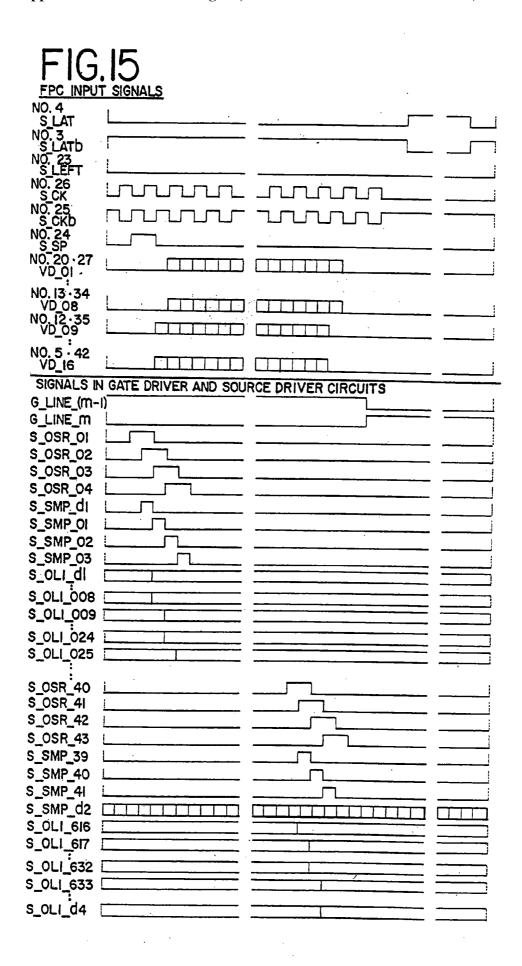

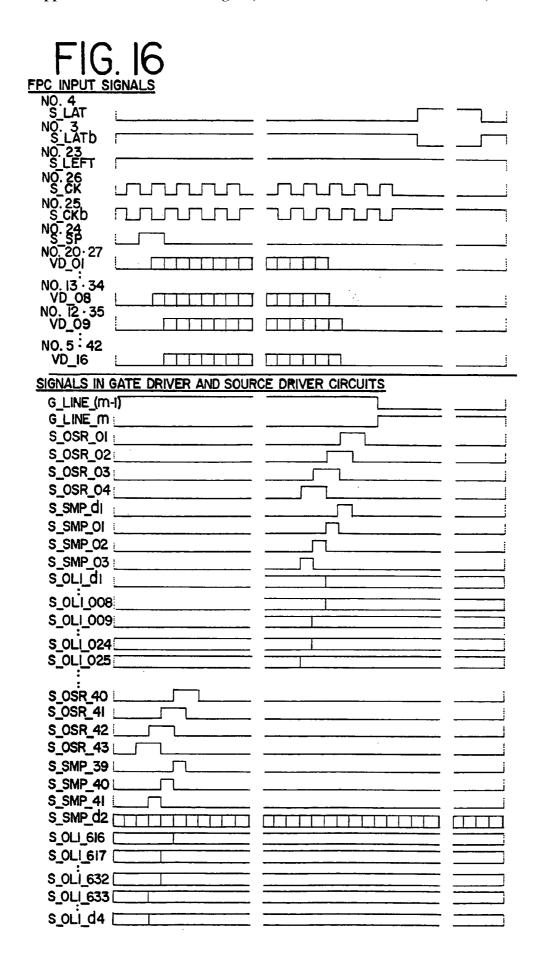

[0066] FIG. 15 is a timing diagram of an input signal from a gate driver circuit side of an EL display device;

[0067] FIG. 16 is a timing diagram of an input signal from a gate driver circuit side of an EL display device;

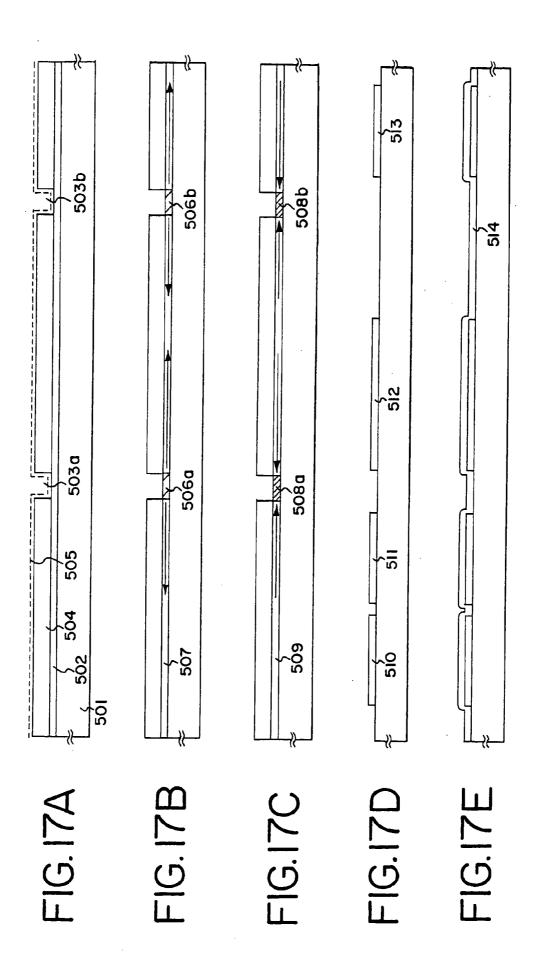

[0068] FIGS. 17A to 17E are diagrams showing a process of manufacturing an EL display device;

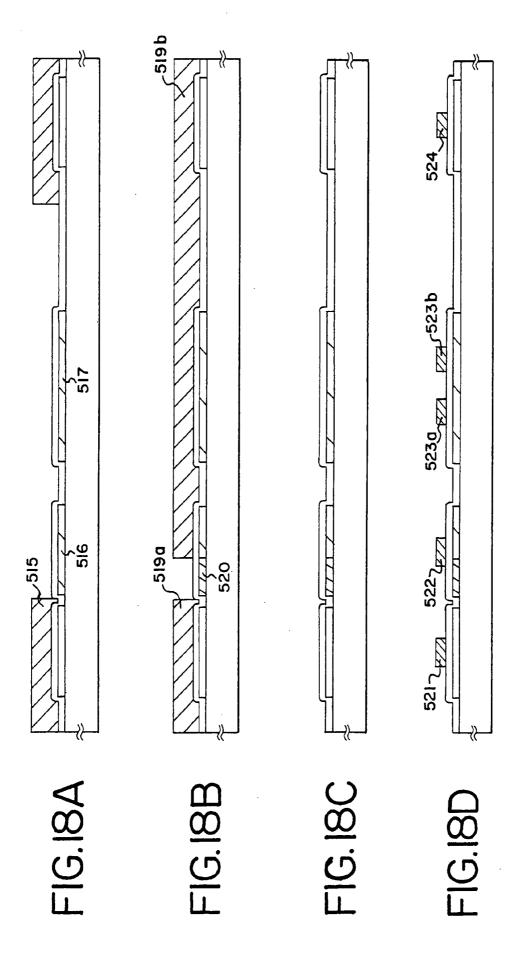

[0069] FIGS. 18A to 18D are diagrams showing the process of manufacturing the EL display device;

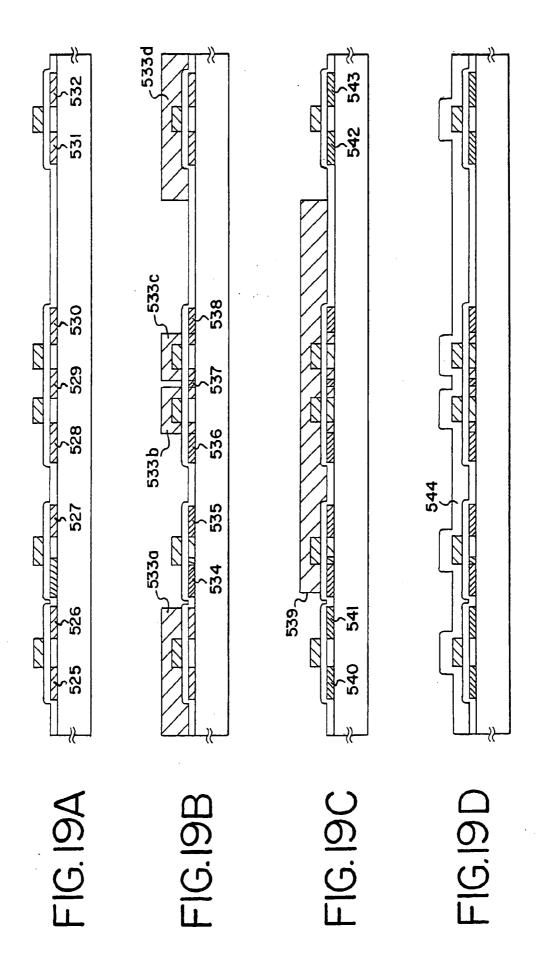

[0070] FIGS. 19A to 19D are diagrams showing the process of manufacturing the EL display device;

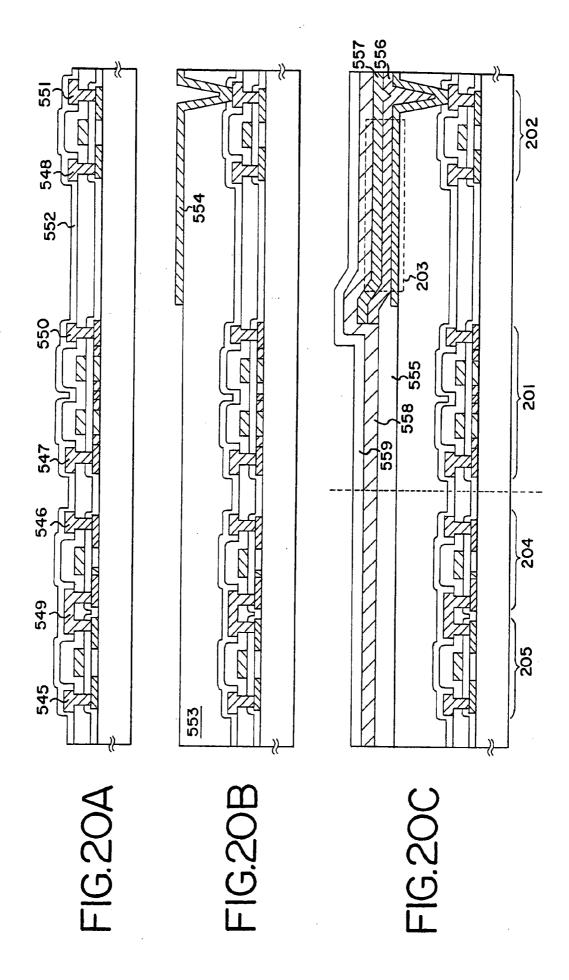

[0071] FIGS. 20A to 20C are diagrams showing the process of manufacturing the EL display device;

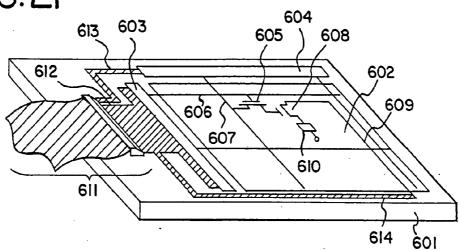

[0072] FIG. 21 is a diagram showing an external view of an EL module;

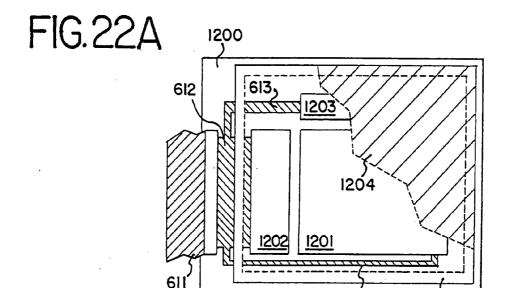

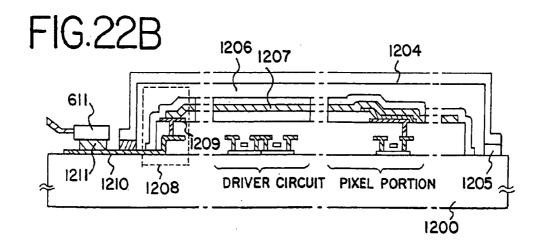

[0073] FIGS. 22A and 22B are diagrams showing an external view of an EL module;

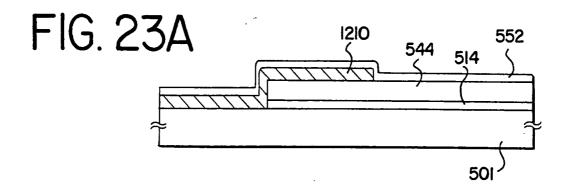

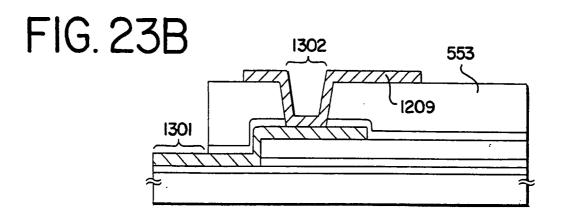

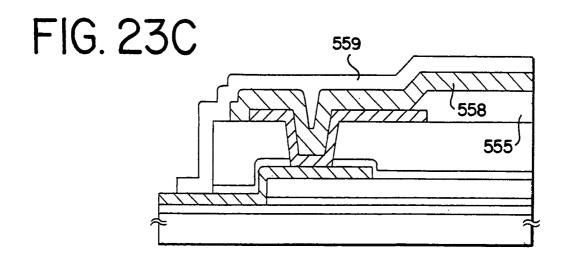

[0074] FIGS. 23A to 23C are diagrams showing a process of manufacturing a contact structure;

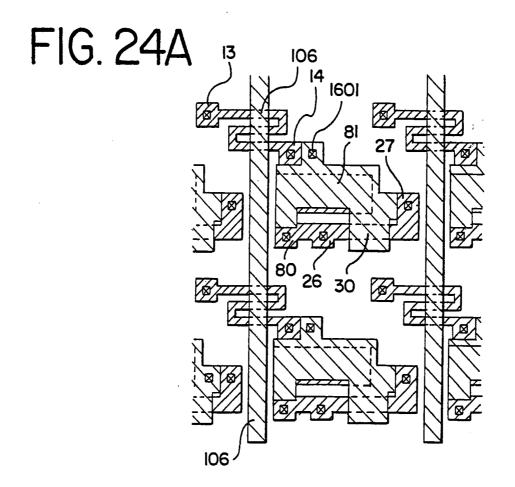

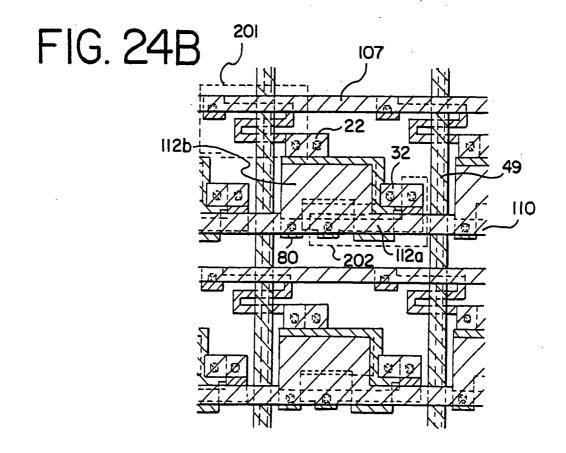

[0075] FIGS. 24A and 24B are diagrams showing a top structure of a pixel portion of an EL display device;

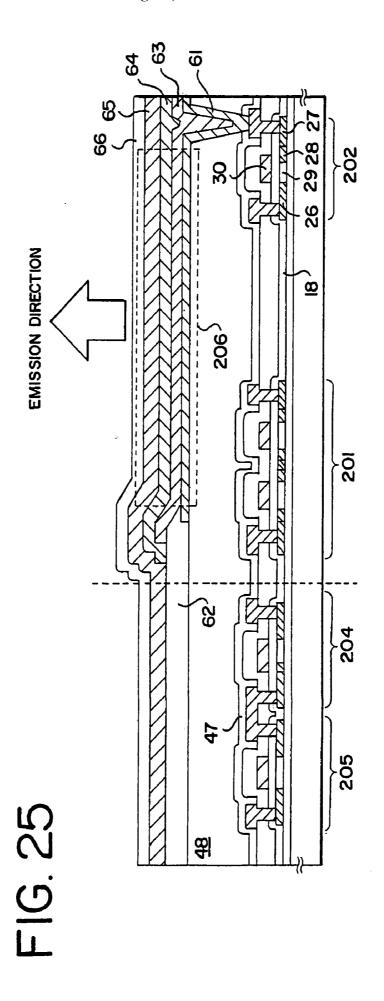

[0076] FIG. 25 is a diagram showing a cross sectional structure of an EL display device;

[0077] FIG. 26 is a diagram showing a portion of a source driver circuit of an EL display device;

[0078] FIGS. 27A and 27B are photographs showing an image of an EL display device which uses the present invention:

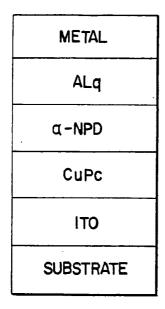

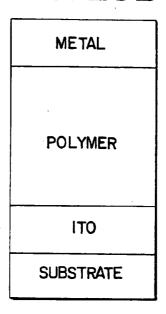

[0079] FIGS. 28A and 28B are diagrams showing an element structure of an EL element;

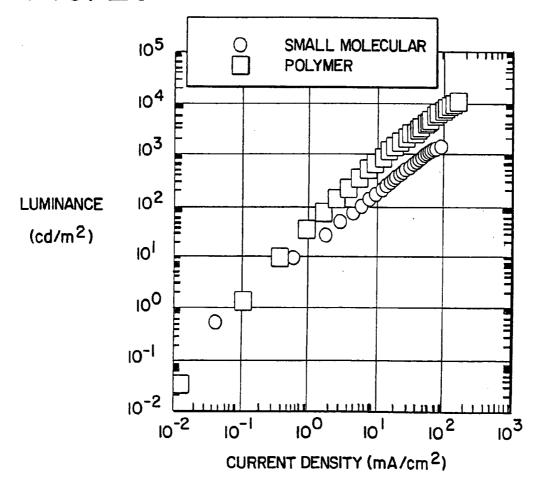

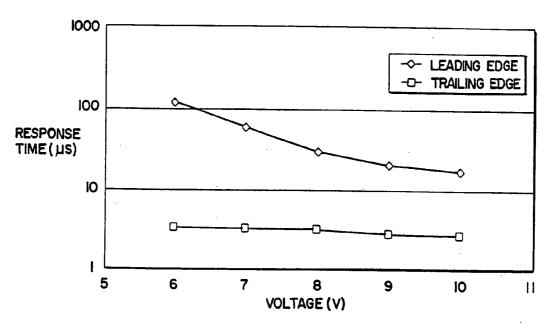

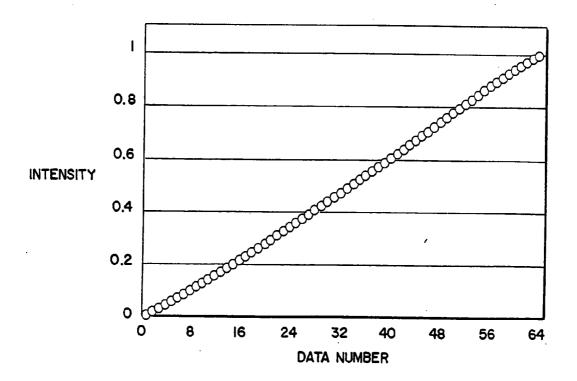

[0080] FIG. 29 is a diagram showing the characteristics of an EL element;

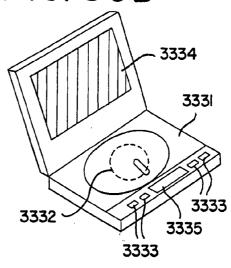

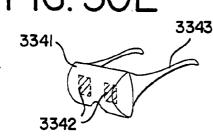

[0081] FIGS. 30A to 30F are diagrams showing specific examples of electronic devices;

[0082] FIGS. 31A to 31C are diagrams showing specific examples of electronic devices;

[0083] FIG. 32 is a diagram showing the characteristics of an EL element;

[0084] FIG. 33 is a diagram showing the characteristics of an EL element;

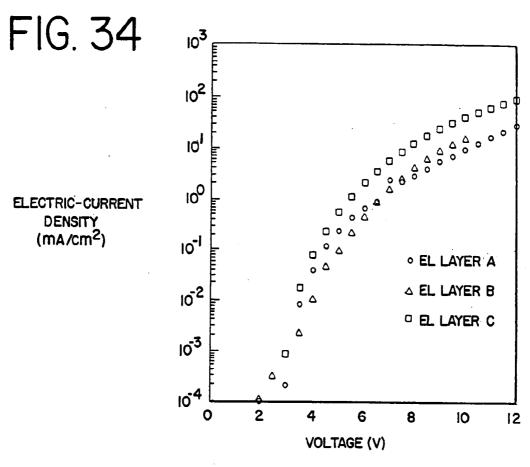

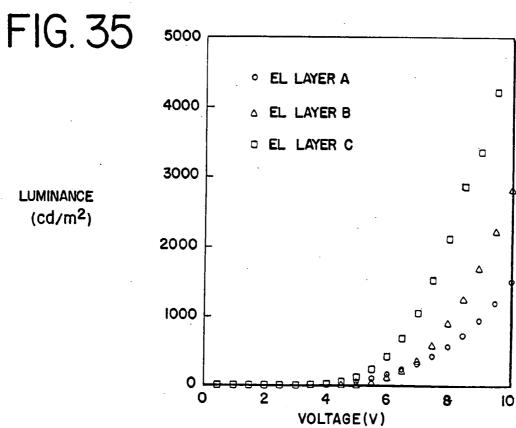

[0085] FIG. 34 is a diagram showing the characteristics of an EL element; and

[0086] FIG. 35 is a diagram showing the characteristics of an EL element.

## DETAILED DESCRIPTION OF THE PREFERRED EMBODIMENTS

[0087] Embodiment Mode

[0088] FIG. 1A is a schematic block diagram of an active matrix type EL display device of the present embodiment. The active matrix type EL display device of FIGS. 1A and 1B is formed by a pixel portion 101, and a source driver circuit 102 and a gate driver circuit 103 arranged in the periphery of a pixel portion by TFTs formed on a substrate. Further, reference numeral 113 denotes a time division gradation data signal generation circuit (SPC, serial to parallel conversion circuit).

[0089] The source driver circuit 102 has a shift register 102a, and a latch (1) 102b, a latch (2) 102c. In addition, it also has a buffer (not shown in the figures).

[0090] Note that only one source driver circuit is formed in the active matrix type EL display device of the present embodiment, but two source driver circuits may be formed so as to sandwich the pixel portion from above and below.

[0091] Furthermore, the gate driver circuit 103 has circuits such as a shift register and a buffer (neither shown in the figures).

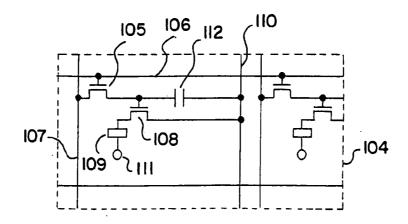

[0092] The pixel portion 101 has 640×480 (horizontalx vertical) pixels. A switching TFT and an electric current control TFT are arranged in each pixel. A switching TFT 105 is connected to a gate line 106 and a source line (data line) 107. Further, a drain of an electric current control TFT 108 is connected to an EL element 109, and a source of the electric current control TFT 108 is connected to an electric current supply line 110.

[0093] A gate of the switching TFT 105 opens when the gate line 106 is selected, a data signal of the source line 107 is stored in the capacitor 112, and a gate of the electric current control TFT 108 opens. In other words, electric current flows in the electric current control TFT 108 due to the data signal input from the source line 107, and the EL element emits light.

[0094] The operation and the signal flow of the active matrix type EL display device of this embodiment mode are explained here.

[0095] The operation of the source driver circuit 102 is explained first. The source driver circuit 102 fundamentally contains the shift register 102a, the latch (1) 102b, and the latch (2) 102c. A clock signal (CK) and a start pulse (SP) are input to the shift register 102a. The shift register 102a generates timing signals in order based on the clock signal (CK) and the start pulse (SP), and the timing signals are

supplied in order to subsequent circuits after passing through the buffer (not shown in the figures).

[0096] The timing signal from the shift register 102a is buffered and amplified by circuits such as the buffer. The load capacitance (parasitic capacitance) is large in the source line which is supplied with the timing signal because there are many circuits or elements connected. The buffer circuit is formed in order to prevent a "blunting" of rise and fall of the generated timing signal because the load capacitance is large.

[0097] The timing signal (Digital Data Signals) which has been buffered and amplified by the buffer is then supplied to the latch (1) 102b. The latch (1) 102b has a latch for processing a six bit digital signal. The latch (1) 102b takes in the six bit digital data signal supplied from a time division gradation data signal generation circuit 113, and stores it, when the above timing signal is input.

[0098] The amount of time until completed for the write-in of the digital data signal to all stages of the latch (1) 102b is referred to as the write-in period. In other words, from the point when the digital data signal in the latch of the stage on the furthest left within the latch (1) 102b is written to the point when the digital data signal in the latch of the rightmost stage is written is the write-in period. Further, the above write-in period is also referred to as a line period.

[0099] After the write-in period is complete, a latch signal is supplied to the latch (2) 102c in accordance with an operation timing of the shift register 102a. At this instant the digital data signal written in and stored in the latch (1) 102b is output all at once to the latch (2) 102c, and stored in the latch (2) 102c.

[0100] Then, after the digital data signal has been sent to the latch (2) 102c, write-in of another digital data signal supplied from the time division gradation data signal generation circuit 113 is again performed in order based upon a timing signal from the shift register 102a.

[0101] Furthermore, a latch signal is input to the latch (2) 102c.

[0102] A timing signal from a shift register (not shown in the figures) is supplied in the gate driver circuit 103, and is supplied to the corresponding gate lines (scanning lines).

[0103] Reference numeral 113 is the time division gradation data signal generation circuit (SPC, serial to parallel conversion circuit). The time division gradation data signal generation circuit 113 is a circuit for reducing the frequency of a digital signal input from the outside to 1/m. By dividing the externally input digital signal, the signal frequency required for operation of the driver circuit can also be reduced to 1/m.

[0104] The data signal input to the pixel portion is a digital signal, and furthermore differing from a liquid crystal display device the present invention is not a voltage gradation display, and therefore the digital data signal having "0" or "1" information is input, as is, to the pixel portion.

[0105] A plurality of pixels 104 are arranged in a matrix state in the pixel portion 101. An enlarged view of the pixel 104 is shown in FIG. 1B. Reference numeral 105 denotes the switching TFT in FIG. 1B, and the switching TFT 105

is connected to the gate line 106 for inputting the gate signal and to the source wiring 107 for inputting the video signal.

[0106] Further, reference numeral 108 is the electric current control TFT, and its gate is connected to the drain of the switching TFT 105. The drain of the electric current control TFT 108 is connected to the EL element 109, and its source is connected to the electric current supply line 110. The EL element 109 is composed of an anode (pixel electrode) connected to the electric current control TFT 108, and a cathode (opposing electrode) formed in opposition to the anode and sandwiching an EL layer, and the cathode is connected to a predetermined electric power supply 111.

[0107] Note that the switching TFT 105 may be an n-channel TFT and may be a p-channel TFT.

[0108] The electric current control TFT has a structure such that when the electric current control TFT 108 is an n-channel TFT, the drain portion of the electric current control TFT 108 is connected to the cathode of the EL element 109, and for a case of using a p-channel TFT for the electric current control TFT 108, the drain portion of the electric current control TFT 108 is connected to the anode of the EL element 109.

[0109] Further, the capacitor 112 is formed in order to store the gate voltage of the electric current control TFT 108 when the switching TFT 105 is in a non-selected state (off state). The capacitor 112 is connected to the drain of the switching TFT 105 and to the electric current supply line 110

[0110] A digital data signal input to the pixel portion as described above is formed by the time division gradation data signal generation circuit 113. This circuit is one in which the video signal made from the digital signal (the signal includes picture information) is transformed into a digital data signal for performing time division gradation, and a circuit in which the timing pulses necessary for performing time division gradation display and the like are generated.

**[0111]** Typically, means for dividing one frame into a plurality of fields corresponding to N bit (where N is an integer greater than or equal to 2) gradations, means for selecting the write-in periods and the display periods in the plurality of fields, and means for setting the display periods so as to become Ts1: Ts2: Ts3: ...: Ts(n-1): Ts(n)= $2^0$ :  $2^{-1}$ :  $2^{-2}$ : ...:  $2^{-(n-2)}$ :  $2^{-(n-1)}$ . are contained in the time division gradation digital signal generation circuit **113**.

[0112] The time division gradation digital signal generation circuit 113 may be formed external to the EL display device of the present invention, and it may also be integrally formed. When forming the circuit external to the EL display device, there is a structure in which the digital data signal formed externally is input to the EL display device of the present invention.

[0113] Next, a schematic of a cross sectional structure of the active matrix EL display device of the present invention is shown in FIG. 2.

[0114] Reference numeral 11 denotes a substrate, and reference numeral 12 denotes an insulating film which becomes a base (hereafter referred to as a base film) in FIG. 2. A substrate transparent to light, typically a glass substrate, a quartz substrate, a glass ceramic substrate, or a crystallized

glass substrate can be used as the substrate 11. Note that the substrate used must be able to withstand the highest processing temperature of the manufacturing process.

[0115] Further, the base film 12 is especially effective for cases in which a substrate containing mobile ions, or a substrate having conductivity is used, but need not be formed for a quartz substrate. An insulating film containing silicon may be used to form the base film 12. Note that the term "insulating film containing silicon" indicates, specifically, an insulating film such as a silicon oxide film, a silicon nitride film, or an oxidized silicon nitride film (denoted by  $SiO_xN_y$ , where x and y are shown by arbitrary integers) containing silicon, oxygen, and nitrogen in predetermined ratios in this specification.

[0116] Reference numeral 201 denotes a switching TFT, formed by an n-channel TFT, but the switching TFT may also be formed as a p-channel TFT. Reference numeral 202 denotes a current control TFT, and FIG. 2 shows a case in which the current control TFT 202 is formed by a p-channel TFT. In other words, the drain electrode of the electric current control TFT is connected to the anode of the EL element in this case. However, the current control TFT is connected to the cathode of the EL element when the electric current control TFT is formed by an n-channel TFT.

[0117] The field effect mobility of the n-channel TFT is larger than the field effect mobility of a p-channel TFT, and therefore large electric current can flow at high speed. Further, even with the same amount of current flow, the TFT size of the n-channel TFT can be made smaller.

[0118] Note that it is not necessary to limit the switching TFT and the current control TFT to n-channel TFTs in the present invention, and that it is possible to use p-channel TFTs for either the switching TFT, the current control TFT, or both.

[0119] The switching TFT 201 is formed having: an active layer containing a source region 13, a drain region 14, LDD regions 15a to 15d, a separating region 16, and channel forming regions 17a and 17b; a gate insulating film 18; gate electrodes 19a and 19b, a first interlayer insulating film 20, a source wiring 21, and a drain wiring 22. Note that the gate insulating film 18 or the first interlayer insulating film 20 may be made common among all TFTs on the substrate, and may also be made to differ corresponding to a circuit or an element

[0120] The switching TFT 201 shown in FIG. 2A has the gate electrodes 19a and 19b electrically connected, becoming a so-called double gate structure. Of course, not only a double gate structure, but a multi-gate structure (a structure containing an active layer having two or more channel forming regions connected in series), such as a triple gate structure, may also be used.

[0121] The multi-gate structure is extremely effective in lowering the value of the off current, and by sufficiently lowering the off current of the switching TFT, it becomes possible to reduce the capacity needed for the capacitor 112 shown in FIG. 1B. Namely, the exclusive surface area of the capacitor 112 can be made smaller, and therefore the multigate structure is also effective in increasing the effective light emitting surface area of the EL element 109.

[0122] In addition, the LDD regions 15a to 15d in the switching TFT 201 are formed sandwiching the gate insu-

lating film 18, and so as not to overlay with the gate electrodes 17a and 17b. This structure is extremely effective in reducing the off current value. Furthermore, the length (width) of the LDD regions 15a to 15d may be set from 0.5 to 3.5  $\mu$ m, typically between 2.0 and 2.5  $\mu$ m.

[0123] Note that the formation of an offset region (a region having the same composition as the channel forming regions, and to which a gate voltage is not applied) between the channel forming regions and the LDD regions is more preferable for reducing the off current value. Further, when a multi-gate structure having two of more gate electrodes is used, the separating region 16 (a region in which the same impurity element is added, and at the same concentration, as that of the source region or the drain region) formed between the channel forming regions is effective in lowering the value of the off current.

[0124] Next, the current control TFT 202 is formed having: a source region 26, a drain region 27, and a channel forming region 29; the gate insulating film 18; a gate electrode 30; the first interlayer insulating film 20; a source wiring 31; and a drain wiring 32. Note that the gate electrode 30 has a single gate structure, but a multi-gate structure may also be used.

[0125] As shown in FIG. 1B, the drain of the switching TFT 201 is electrically connected to the gate of the current control TFT 202. Specifically, the gate electrode 30 of the current control TFT 202 is electrically connected to the drain region 14 of the switching TFT 201 through the drain wiring (also referred to as a connection wiring) 22. Further, the source wiring 31 is connected to an electric current supply wiring 110 in FIG. 1B.

[0126] Further, looking from the viewpoint of increasing the amount of current that is able to flow, it is also effective to make the film thickness of the active layer (especially the channel forming region) of the current control TFT 202 thick (preferably from 50 to 100 nm, more preferably between 60 and 80 nm). Conversely, looking from the point of view of making the off current value smaller for the switching TFT 201, it is also effective to make the film thickness of the active layer (especially the channel forming region) thin (preferably from 20 to 50 nm, more preferably between 25 and 40 nm).

[0127] The structure of the TFT formed within the pixel is explained above, but a driver circuit is also formed at the same time. A CMOS circuit, the basic unit forming the driver circuit, is shown in FIG. 2.

[0128] In FIG. 2, a TFT having a structure which reduces hot carrier injection as much as possible, without dropping the operation speed, is used as an n-channel TFT 204 of the CMOS circuit. Note that the driver circuit referred to here indicates the source driver circuit 102 and the gate signal driver circuit 103 shown in FIG. 1A. It is also possible to form other signal processing circuit, of course (such as a level shifter, an A/D converter, or a signal divider circuit).

[0129] An active layer of the n-channel TFT 204 contains a source region 35, a drain region 36, an LDD region 37, and a channel forming region 38, and the LDD region 37 overlaps a gate electrode 39, sandwiching the gate insulating film 18. The LDD region 37 is referred to as an Lov region throughout this specification.

[0130] The formation of the LDD region on only the drain region side is in consideration of not lowering the operation speed. Further, it is not necessary to be very concerned with the value of the off current in the n-channel TFT 204, and greater emphasis should be placed on the operation speed. It is therefore preferable that the LDD region 37 completely overlaps the gate electrode, reducing resistive components as much as possible. In other words, it is good to eliminate all offset.

[0131] Deterioration by hot carrier injection of a p-channel TFT 205 of the CMOS circuit is almost of no concern, and in particular, an LDD region need not be formed. The active layer therefore contains a source region 40, a drain region 41, and a channel forming region 42, and the gate insulating film 18 and a gate electrode 43 are formed on top. It is also possible, of course, to take action against hot carriers by forming an LDD region similar to that of the n-channel TFT 204.

[0132] Further, the n-channel TFT 204 and the p-channel TFT 205 are each covered by the first interlayer insulating film 20, and source wirings 44 and 45 are formed. In addition, both are electrically connected by a drain wiring 46

[0133] Next, reference numeral 47 denotes a first passivation film, and its film thickness may be set from 10 nm to 1  $\mu$ m (preferably between 200 and 500 nm). An insulating film containing silicon (in particular, it is preferable to use an oxidized silicon nitride film or a silicon nitride film) can be used as the passivation film material. The passivation film 47 possesses a role of protecting the formed TFTs from alkaline metals and moisture. In the final EL layer to be provided on the upper part of the TFT, alkaline metal such as sodium is included. In other words, the first passivation film 47 works also as a protecting layer so that these alkaline metals (mobile ions) do not penetrate into the TFT. However, it is not always necessary to form this passivation film, and when necessary, it may be formed.

[0134] Further, reference numeral 48 denotes a second interlayer insulating film, which has a function as a leveling film for performing leveling of a step due to the TFTs. An organic resin film is preferable as the second interlayer insulating film 48, and one such as polyimide, polyamide, acrylic, or BCB (benzocyclobutene) may be used. These organic resin films have the advantages of easily forming a good, level surface, and having a low specific dielectric constant. The EL layer is extremely sensitive to unevenness, and therefore it is preferable to nearly absorb all the TFT step by the second interlayer insulating film. In addition, it is preferable to form the low specific dielectric constant material thickly for reducing the parasitic capacitance formed between a gate wiring or data wiring and the cathode of the EL element. The thickness, therefore, is preferably from 0.5 to 5  $\mu$ m (more preferably between 1.5 and 2.5  $\mu$ m).

[0135] Further, reference numeral 49 denotes a pixel electrode made from a transparent conducting film. After opening a contact hole in the second interlayer insulating film 48 and in the first passivation film 47, the pixel electrode 49 is formed so as to be connected to the drain wiring 32 of the

current control TFT 202. Note that if the pixel electrode 49 and the drain region 27 are directly connected, as in FIG. 2, then alkaline metals of the EL layer can be prevented from entering the active layer via the pixel electrode.

[0136] A third interlayer insulating film 50 is formed on the pixel electrode 49 from a silicon oxide film, an oxidized silicon nitride film, or an organic resin film, with a thickness from 0.3 to 1  $\mu$ m. An open portion is formed in the third interlayer insulating film 50 over the pixel electrode 49 by etching, and the edge of the open portion is etched so as to become a tapered shape. The taper angle may be set from 10 to 60°, (preferably between 30 and 50°).

[0137] An EL layer 51 is formed on the third interlayer insulating film 50. A single layer structure or a lamination structure can be used for the EL layer 51, but the lamination structure has good light emitting efficiency. In general, a hole injecting layer, a hole transporting layer, an emitting layer, and an electron transporting layer are formed in order on the pixel electrode, but a structure having a hole transporting layer, an emitting layer, and an electron transporting layer, or a structure having a hole injecting layer, a hole transporting layer, an emitting layer, an electron transporting layer, and an electron injecting layer may also be used. Any known structure may be used in the present invention, and doping of a fluorescing pigment and the like into the EL layer may also be performed.

[0138] Known materials can be used as the organic EL materials, and for example, the materials disclosed in the following U.S. Patents and Japanese patent applications can be used: U.S. Pat. No. 4,356,429; U.S. Pat. No. 4,539,507; U.S. Pat. No. 4,720,432; U.S. Pat. No. 4,769,292; U.S. Pat. No. 4,885,211; U.S. Pat. No. 4,950,950; U.S. Pat. No. 5,059,861; U.S. Pat. No. 5,047,687; U.S. Pat. No. 5,073,446; U.S. Pat. No. 5,059,862; U.S. Pat. No. 5,061,617; U.S. Pat. No. 5,151,629; U.S. Pat. No. 5,294,869; U.S. Pat. No. 5,294,870; Japanese Patent Application Laid-open No. Hei 8-241048; and Japanese Patent Application Laid-open No. Hei 8-78159.

[0139] Note that EL display devices are roughly divided into four types of color display methods: a method of forming three types of EL elements corresponding to R, G, and B; a method of combining white color luminescing EL elements with color filters; a method of combining blue or blue-green luminescing EL elements and fluorescent matter (fluorescing color change layer, CCM); and a method of using a transparent electrode as a cathode (opposing electrode) and overlapping EL elements corresponding to R, G, and B

[0140] The structure of FIG. 2 is an example of a case of forming three types of EL elements corresponding to R, G, and B. Note that although only one pixel is shown in FIG. 2, pixels having an identical structure are formed corresponding to red, green and blue colors, respectively, and that color display can thus be performed.

[0141] It is possible to implement the present invention without regard to the method of luminescence, and all of the above four methods can be used in the present invention.

However, compared with EL, a fluorescing body has the problems of slow response speed and afterglow, and therefore it is preferable to not use a fluorescing body. Further, it is also preferable to not use any color filters, which becomes the cause of the brightness of the emitted light to drop.

[0142] A cathode 52 of an EL element is formed on the EL layer 51. A material containing a low work coefficient material such as magnesium (Mg), lithium (Li), or calcium (Ca), is used as the cathode 52. Preferably, an electrode made from MgAg (a material made from Mg and Ag at a mixture of Mg:Ag=10:1) is used. In addition, a MgAgAl electrode, an LiAl electrode, and an LiFAl electrode can be given as other examples.

[0143] It is preferable to form the cathode 52 in succession, without exposure to the atmosphere, after forming the EL layer 51. This is because the interface state between the cathode 52 and the EL layer 51 greatly influences the light emitting efficiency of the EL element. Note that, throughout this specification, a light emitting element formed by a pixel electrode (anode), an EL layer, and a cathode is referred to as an EL element.

[0144] The lamination body composed of the EL layer 51 and the cathode 52 need to be formed separately for each pixel, but the EL layer 51 is extremely weak with respect to moisture, and therefore a normal photolithography technique cannot be used. It is therefore preferable to use a physical mask material such as a metal mask, and to selectively form the layers by a gas phase method such as vacuum evaporation, sputtering, or plasma CVD.

[0145] Note that it is also possible to use a method such as ink jet printing or screen printing as the method of selectively forming the EL layer. However, the cathode cannot currently be formed in succession with these methods, and therefore it seems preferable to use the other methods stated above.

[0146] Further, reference numeral 53 denotes a protecting electrode, which protects the cathode 52 from external moisture and the like at the same time is an electrode for connecting to the cathode 52 of each pixel. It is preferable to use a low resistance material containing aluminum (Al), copper (Cu), or silver (Ag) as the protecting electrode 53. The protecting electrode 53 can also be expected to have a heat radiating effect which relieves the amount of heat generated by the EL layer. In addition, it is effective to form the protecting electrode 53 in succession, without exposure to the atmosphere, after forming the above EL layer 51 and the cathode 52.

[0147] Further, reference numeral 54 denotes a second passivation film, and the film thickness may be set from 10 nm to  $1\mu$ m (preferable between 200 and 500 nm). The aim of forming the second passivation film is mainly in order to protect the EL layer 51 from moisture, but it is also effective if it is given a heat radiating effect. Note that the above stated EL layer is weak with respect to heat, and therefore it is preferable for film deposition to be performed at as low a temperature as possible (preferably in a temperature range from room temperature to 120° C.). Therefore plasma CVD, sputtering, vacuum evaporation, ion plating, and solution

application (spin coating) are preferable methods of film deposition. However, it is not always necessary to form the second passivation film **54**, and when required, it should be formed.

[0148] The main point of the present invention is to improve on the problem of dispersion in TFT characteristics, which has become a problem in analog drive gradation up to now, changing the analog drive gradation display to a digital drive time division gradation display in an active matrix type EL display device. Therefore, the present invention is not limited to the structure of the EL display device of FIG. 2, and the structure of FIG. 2 is only one preferable form of implementing the present invention.

[0149] The above TFTs using a polysilicon film have high speed operation, but easily deteriorate due to causes such as hot carrier injection. Therefore, as shown in FIG. 2, the formation of TFTs within the pixel having a structure which differs in response to their function (the switching TFT with sufficiently low off current and the electric current control TFT which is strong with respect to hot carrier injection) provides high reliability. Further, it is extremely effective in the manufacture of an EL display device capable of good image display (good motion functionality).

[0150] Embodiment 1

[0151] An embodiment of the present invention is explained using FIGS. 9 to 16 and Tables 1 to 4.

[0152] A pixel portion used when implementing the present invention, a circuit structure and specifications (such as size and voltage values) of a driver formed in the periphery of the pixel portion, and an input signal are explained here.

[0153] FIG. 9 is a plane diagram of a complete panel as seen from above (from a cathode film deposition side). Display is performed facing the bottom. Reference numeral 901 in FIG. 9 denotes a pixel portion, reference numeral 902 denotes a source driver circuit, 903 denotes a gate driver circuit, and 904 denotes an input portion of a flexible printed circuit (hereafter referred to as FPC). Note that the FPC input portion 904 used in embodiment 1 has 50 terminals at a 300  $\mu$ m pitch.

[0154] The FPC input portion 904 of FIG. 9 in embodiment 1 has a circuit for protecting the FPC input portion, as shown in FIG. 10. Note that video signal input terminals (terminals 5 to 20 and 27 to 42 from among terminals 1 to 50 attached in the upper portion of the FPC input portion 904 in FIG. 9) do not have resistors (R1).

[0155] Note also that the portions of the FPC input terminal portion having the protecting circuit are all numbers 1 to 50 attached in the top portion of the FPC input portion 904 in FIG. 9, except for numbers 1, 2, 21, 22, 43, 44, 49, and 50.

[0156] In addition, Table 1 shows the specifications of the FPC input terminals used in embodiment 1. Note that the term "terminal No." shown in Table 1 corresponds to the numbers 1 to 50 attached to the top portion of the FPC input portion 904 in FIG. 9.

TABLE 1

| Terminal<br>No. | Terminal<br>Symbol | Signal Type            | Voltage Range [V]              | Notes (Name of Signals etc.)                                                                     |  |

|-----------------|--------------------|------------------------|--------------------------------|--------------------------------------------------------------------------------------------------|--|

| 1               | EL_CATH            | NC<br>Unbalance        | approximately<br>4 (0.0~9.0)/9 | Pad only<br>EL Driver D.C. Power Source (Cathode)                                                |  |

| 2               | EL_ANOD            | Power Source           | 9`                             | EL Driver D.C. Power Source (Anode)                                                              |  |

| 3               | S_LATb             | Unbalance              | 0.0/9.0                        | Source Driver Circuit Latch Inverted Signal                                                      |  |

| 4               | S_LAT              | Unbalance              | 0.0/9.0                        | Source Driver Circuit Latch Signal                                                               |  |

| 5               | VD_16              | Unbalance              | 0.0/9.0                        | Digital Video Signal 16                                                                          |  |

| 6               | VD_15              | Unbalance              | 0.0/9.0                        | Digital Video Signal 15                                                                          |  |

| 7               | VD_14              | Unbalance              | 0.0/9.0                        | Digital Video Signal 14                                                                          |  |

| 8               | VD_13              | Unbalance              | 0.0/9.0                        | Digital Video Signal 13                                                                          |  |

| 9               | VD_12              | Unbalance              | 0.0/9.0                        | Digital Video Signal 12                                                                          |  |

| 10              | VD_11              | Unbalance              | 0.0/9.0                        | Digital Video Signal 11                                                                          |  |

| 11              | VD_10              | Unbalance              | 0.0/9.0                        | Digital Video Signal 10                                                                          |  |

| 12              | <b>V</b> D_09      | Unbalance              | 0.0/9.0                        | Digital Video Signal 9                                                                           |  |

| 13              | VD_08              | Unbalance              | 0.0/9.0                        | Digital Video Signal 8                                                                           |  |

| 14              | VD_07              | Unbalance              | 0.0/9.0                        | Digital Video Signal 7                                                                           |  |

| 15              | <b>V</b> D_06      | Unbalance              | 0.0/9.0                        | Digital Video Signal 6                                                                           |  |

| 16              | VD_05              | Unbalance              | 0.0/9.0                        | Digital Video Signal 5                                                                           |  |

| 17              | VD_04              | Unbalance              | 0.0/9.0                        | Digital Video Signal 4                                                                           |  |

| 18              | VD_03              | Unbalance              | 0.0/9.0                        | Digital Video Signal 3                                                                           |  |

| 19              | VD_02              | Unbalance              | 0.0/9.0                        | Digital Video Signal 2                                                                           |  |

| 20              | VD_01              | Unbalance              | 0.0/9.0                        | Digital Video Signal 1                                                                           |  |

| 21              | S_GND              | Power Source           | 0                              | Source Driver Circuit Negative Power Source                                                      |  |

| 22              | S_VDD              | Power Source           | 9                              | Source Driver Circuit Positive Power<br>Source                                                   |  |

| 23              | S_LEFT             | Power Source           | 0.0 or 9.0                     | Source Driver Circuit Scanning Direction<br>Selector (0.0: Right Scanning 9.0: Left<br>Scanning) |  |

| 24              | S_SP               | Unbalance              | 0.0/9.0                        | Source Driver Circuit Start Pulse Signal                                                         |  |

| 25              | S_CKb              | Balance                | 0.0/9.0                        | Source Driver Circuit Clock Inverted Signal                                                      |  |

| 26              | S_CK               | Balance                | 0.0/9.0                        | Source Driver Circuit Clock Signal                                                               |  |

| 27              | VD_01              | Unbalance              | 0.0/9.0                        | Digital Video Signal 1                                                                           |  |

| 28              | VD_02              | Unbalance              | 0.0/9.0                        | Digital Video Signal 2                                                                           |  |

| 29              | VD_03              | Unbalance              | 0.0/9.0                        | Digital Video Signal 3                                                                           |  |

| 30              | VD_04              | Unbalance              | 0.0/9.0                        | Digital Video Signal 4                                                                           |  |

| 31              | VD_05              | Unbalance              | 0.0/9.0                        | Digital Video Signal 5                                                                           |  |

| 32              | VD_06              | Unbalance              | 0.0/9.0                        | Digital Video Signal 6                                                                           |  |

| 33              | VD_07              | Unbalance              | 0.0/9.0                        | Digital Video Signal 7                                                                           |  |

| 34<br>25        | VD_08              | Unbalance              | 0.0/9.0                        | Digital Video Signal 8                                                                           |  |

| 35<br>36        | VD_09              | Unbalance<br>Unbalance | 0.0/9.0                        | Digital Video Signal 9<br>Digital Video Signal 10                                                |  |

| 37              | VD_10<br>VD_11     | Unbalance              | 0.0/9.0<br>0.0/9.0             | Digital Video Signal 10 Digital Video Signal 11                                                  |  |

| 38              | VD_11<br>VD_12     | Unbalance              | 0.0/9.0                        | Digital Video Signal 12                                                                          |  |

| 39              | VD_12<br>VD_13     | Unbalance              | 0.0/9.0                        | Digital Video Signal 12 Digital Video Signal 13                                                  |  |

| 40              | VD_13<br>VD_14     | Unbalance              | 0.0/9.0                        | Digital Video Signal 14                                                                          |  |

| 41              | VD_15              | Unbalance              | 0.0/9.0                        | Digital Video Signal 15                                                                          |  |

| 42              | VD_16              | Unbalance              | 0.0/9.0                        | Digital Video Signal 16                                                                          |  |

| 43              | G_GND              | Power Source           | 0                              | Gate Driver Circuit Negative Power Source                                                        |  |

| 44              | G_VDD              | Power Source           | 10                             | Gate Driver Circuit Positive Power Source                                                        |  |

| 45              | G_UP               | Power Source           | 0.0 or 10.0                    | Gate Driver Circuit Scanning Direction                                                           |  |

|                 |                    |                        |                                | Selector (0.0: Down Scanning 9.0: Up<br>Scanning)                                                |  |

| 46              | G_CKb              | Balance                | 0.0/10.0                       | Gate Driver Circuit Clock Inverted Signal                                                        |  |

| 47              | G_CK               | Balance                | 0.0/10.0                       | Gate Driver Circuit Clock Signal                                                                 |  |

| 48              | G_SP               | Unbalance              | 0.0/10.0                       | Gate Driver Circuit Start pulse Signal                                                           |  |

| 49              | EL_ANOD            | Power Source           | 9                              | EL Driver D.C. Power Source (Anode)                                                              |  |

| 50              | EL_ANOD<br>EL_CATH | Unbalance              | approximately                  | EL Driver D.C. Power Source (Cathode)                                                            |  |

|                 |                    | NC                     | 4 (0.0~9.0)/9                  | Pad only                                                                                         |  |

[0157] Next, FIG. 11 shows a detailed circuit diagram of the gate driver circuit 903 of FIG. 9. A positive electric power supply voltage in the gate driver circuit is 10 V, and a negative electric power supply voltage is 0 V. The operation clock frequency input to the gate driver circuit is 232

kHz. Further, the gate driver circuit has a function for switching between scanning directions.

[0158] Symbol g\_chsw\_a in FIG. 11 is a scanning direction switch, symbols g\_sftr\_b, g\_sftr\_c, and g\_sftr\_d are

portions of a shift register, symbol g\_nand\_e is a NAND circuit, and symbol g\_buff\_f denotes a buffer.

[0159] A portion enclosed by a dashed line in FIG. 11, namely a portion composed of g\_chsw\_a, g\_sftr\_b, g\_sftr\_c, and g\_sftr\_d, is referred to as a shift register 11001 in embodiment 1.

[0160] The size of the TFTs contained in the shift register, the NAND circuit, the buffer structuring the gate driver circuit of embodiment 1 are shown in Table 2.

[0161] P-type TFTs and n-type TFTs are used in the shift register, the NAND circuit, and the buffer, and therefore values are shown for each of the TFTs. The sizes in Table 2 correspond to the symbols shown in FIG. 10. Further, symbol L ( $\mu$ m) in the table denotes the channel length of the TFT, and symbol W ( $\mu$ m) denotes the TFT channel width. Note that the Lov region is contained in the channel length of the n-type TFT.

TABLE 2

| Pch-TFT                                                              | L[µm]                                  | W[µm]                            | Nch-TFT                                               | L<br>[ <i>μ</i> m]         | Lov[µm]                         | W<br>[μm]                      |

|----------------------------------------------------------------------|----------------------------------------|----------------------------------|-------------------------------------------------------|----------------------------|---------------------------------|--------------------------------|

| g_chsw_a<br>g_sftr_b<br>g_sftr_c<br>g_sftr_d<br>g_nand_e<br>g_buff_f | 4.5<br>4.5<br>4.5<br>4.5<br>4.5<br>4.5 | 20<br>16<br>40<br>10<br>22<br>50 | g_chsw_a g_sftr_b g_sftr_c g_sftr_d g_nand_e g_buff_f | 5<br>5<br>5<br>5<br>5<br>5 | 0.5<br>0.5<br>0.5<br>0.5<br>0.5 | 10<br>8<br>20<br>5<br>22<br>25 |

[0162] Next, a detailed circuit diagram of the source driver circuit 902 of FIG. 9 is shown in FIG. 12. A positive electric power supply voltage in the source driver circuit is 9 V, and a negative electric power supply voltage is 0 V. The operation clock frequency input to the source driver circuit is 12.5 MHz and the source driver circuit has a function for switching between scanning directions.

[0163] Symbol s\_chsw\_a in FIG. 12 is a scanning direction switch, symbols s\_sftr\_b, s\_sftr\_c, and s\_sftr\_d are portions of a shift register, symbol s\_nand\_e is a NAND circuit, and symbols s\_buff\_f, s\_buff\_g, S\_buff\_h, and s\_buff\_i all denote buffers. Further, symbols s\_lat1\_j, s\_lat1\_k, s\_lat1\_m, s\_lat\_n are latches on the first row (hereinafter referred to as latch 1), and s\_lat2\_p, s\_lat2\_r, s\_lat2\_s are latches on the second row (hereinafter referred to as latch 2).

[0164] A portion enclosed by a dashed line in FIG. 12, namely a portion composed of s\_chsw\_a, s\_sftr\_b, s\_sftr\_c, and s\_sftr\_d, is referred to as a shift register 12001 in embodiment 1.

[0165] The size of the TFTs contained in the shift register, the NAND circuit, the buffer structuring the source driver circuit of embodiment 1 are next shown in Table 3. P-type TFTs and n-type TFTs are used in the shift register, the NAND circuit, and the buffer, and therefore values are shown for each of the TFTs. The sizes in Table 3 correspond to each of the symbols shown in FIG. 12. Further, symbol L  $(\mu m)$  in the table denotes the channel length of the TFT, and symbol W  $(\mu m)$  denotes the TFT channel width. Note that the Lov region is contained in the channel length of the n-type TFT.

TABLE 3

| Pch-TFT  | Ц[ <i>µ</i> m] | W[µm] | Nch-TFT  | L<br>[ <i>μ</i> m] | Lov[µm] | W<br>[μm] |

|----------|----------------|-------|----------|--------------------|---------|-----------|

| s_chsw_a | 4.5            | 60    | s_chsw_a | 5                  | 0.5     | 40        |

| s_sftr_b | 4.5            | 50    | s_sftr_b | 5                  | 0.5     | 25        |

| s_sftr_c | 4.5            | 100   | s_sftr_c | 5                  | 0.5     | 50        |

| s_sftr_d | 4.5            | 30    | s_sftr_d | 5                  | 0.5     | 15        |

| s_nand_e | 4.5            | 50    | s_nand_e | 5                  | 0.5     | 50        |

| s_buf1_f | 4.5            | 100   | s_buf1_f | 5                  | 0.5     | 50        |

| s_buf1_g | 4.5            | 100   | s_buf1_g | 5                  | 0.5     | 50        |

| s_buf1_h | 4.5            | 300   | s_buf1_h | 5                  | 0.5     | 150       |

| s_buf1_i | 4.5            | 400   | s_buf1_i | 5                  | 0.5     | 200       |

| s_lat1_j | 4.5            | 16    | s_lat1_j | 5                  | 0.5     | 8         |

| s_lat1_k | 4.5            | 16    | s_lat1_k | 5                  | 0.5     | 8         |

| s_lat1_m | 4.5            | 4     | s_lat1_m | 5                  | 0.5     | 2         |

| s_buf2_n | 4.5            | 30    | s_buf2_n | 5                  | 0.5     | 15        |

| s_lat2_p | 4.5            | 16    | s_lat2_p | 5                  | 0.5     | 8         |

| s_lat2_r | 4.5            | 16    | s_lat2_r | 5                  | 0.5     | 8         |

| s_lat2_s | 4.5            | 4     | s_lat2_s | 5                  | 0.5     | 2         |

| s_buf3_t | 4.5            | 30    | s_buf3_t | 5                  | 0.5     | 15        |

[0166] Timing charts for signals input from the gate driver circuit are shown in FIG. 13 and FIG. 14. FIG. 13 is for a case in which the gate line selection is in the downward scanning direction, and FIG. 14 is for a case of the upward scanning direction. Note that this is shown with a unit of one field.

[0167] A signal input from the FPC and a signal input from the gate driver circuit are shown in FIG. 13 and FIG. 14. In the signal input from the FPC, symbol EL\_CATH is a dc power supply for driving the EL, symbol G\_UP is a signal for switching the scanning direction of the gate driver circuit, symbol G\_CK is a clock signal input to the gate driver circuit, symbol G\_CKb is an inverted clock signal input to the gate driver circuit, and symbol G\_SP denotes a start pulse signal input to the gate driver circuit.

[0168] Furthermore, in the signal input from the gate driver circuit, symbols such as G\_OSR\_001 denote a signal output from the shift registers, and symbols such as G\_LINE\_001 denote a signal input to the gate lines.

[0169] The symbols shown in FIG. 13 and FIG. 14 correspond to the symbols shown in FIG. 11.

[0170] Next, timing charts for signals input from the source driver circuit are shown in FIG. 15 and FIG. 16. Both are for horizontal direction scanning, and FIG. 15 is for a case of writing into m columns of pixels by scanning in the right direction, while FIG. 16 is for a case of writing into m columns of pixels by scanning in the left direction.

[0171] A signal input from the FPC and a signal input from the gate driver circuit and the source driver circuit are shown in FIG. 15 and FIG. 16. In the signal input from the FPC, symbol S\_LAT is a latch signal input to the source driver circuit, symbol S\_LAT is an inverted latch signal input to the source driver circuit, symbol S\_LEFT is a signal for switching the scanning direction of the source driver circuit, symbol S\_CK is a clock signal input to the source signal circuit, symbol S\_CKb is an inverted clock signal input to the source driver circuit, symbol S\_SP is a start pulse signal input to the source driver circuit, and symbols such as VD\_01 denote a video signal input to the source driver circuit from the first (number 01) of 16 video lines.

[0172] Furthermore, in the signal input from the source driver circuit, symbols such as S\_OSR\_001 denote a signal

output from the shift registers to the source line, and symbols such as S\_OL1\_01 denote a signal output from the latch 1 connected to the first (number 001) source line. Symbols such as S\_SMP\_01 denote a signal output from the sampling circuit connected to the first (number 01) source line. Symbols such as G\_LINE\_m denote a signal input to the number m gate line.

[0173] The symbols shown in FIG. 15 and FIG. 16 correspond to the symbols shown in FIG. 12.

[0174] Each pixel inside the panel in embodiment 1 has a structure like that of reference numeral 71 of FIG. 7. The EL driver TFT 702 is p-type (L=5  $\mu$ m, W=2  $\mu$ m), and the pixel switch TFT 701 is n-type (L=2.5T (excluding Loff=0.5×2×3), W=1  $\mu$ m). Further, the surface area of the supplemental capacitor 704 is S=from 0.05 to 0.11 mm<sup>2</sup>.

[0175] The specifications of a display panel in embodiment 1 are shown in Table 4.

## TABLE 4

| Screen Size                       | 0.7 inch (diagonal) |

|-----------------------------------|---------------------|

| Number of Pixels                  | 640 × 480           |

| Pixel Space                       | 22.5 $\mu$ m        |

| Gradation                         | 64 (6 bit)          |

| Aperture Ratio                    | 38%                 |

| Operating Clock frequency in      | 12.5 MHz            |

| Source Driver Circuit             |                     |

| Operating Clock frequency in Gate | 232 kHz             |

| Driver Circuit                    |                     |

| Voltage in Driver Circuit         | 9 <b>V</b>          |

| Voltage in Display Portion        | 7 V                 |

| Duty Ratio                        | 62.5%               |

| Color                             | Single Color        |

|                                   |                     |

[0176] the panel size in embodiment 1 is 50 mm×50 mm, and the screen size is 14.4 mm×10.8 mm (0.7 inch diagonal). The pixel size is 12.5  $\mu$ m×12.5  $\mu$ m, the pixel matrix has a striped shape, and the aperture ratio is approximately 38%.

[0177] Further, the number of pixels per one screen is calculated by  $(d2+640+d2)\times(d2+480+d2)$ , which equals 307,200+(d)4496 pixels (where d refers to a dummy).

[0178] The panel specifications in embodiment 1 are a 640×480 VGA, and a single color display. Further, there are 64 gradations (6 bits), and the duty ratio is 62.5%.

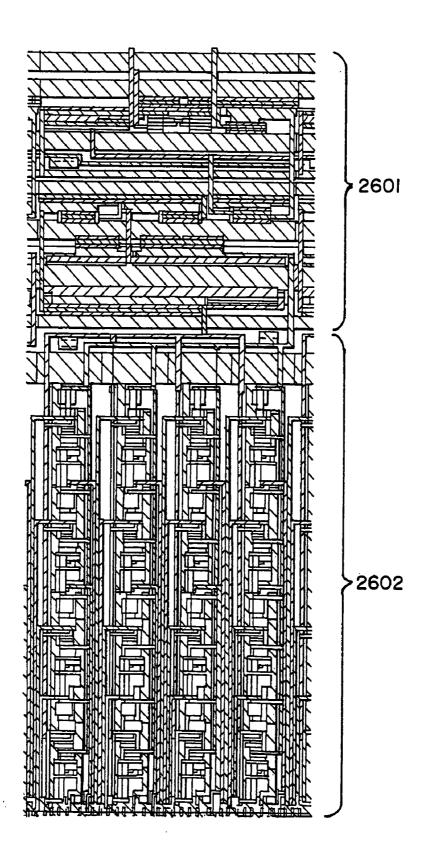

[0179] A portion of the source driver circuit in embodiment 1 is shown in FIG. 26. Reference numeral 2601 in the figure denotes a shift register, and reference numeral 2602 denotes a latch (1).

[0180] In addition, a photograph of a static image display of the EL display device obtained by implementing the present invention is shown in FIG. 27.

[0181] Embodiment 2

[0182] A switch (reference numeral 709 of FIG. 7) of a power supply for applying a voltage to an EL element formed externally to the panel is turned off during a display period, and the power supply switch is turned on during a write-in period in embodiment 1. If this method is used, it becomes a system in which the electric power supply switch is turned on at the same time as the display period is entered, after the write-in period is finished. In this case a large, sudden increase in the amount of electric current develops at

the same time as the display period is entered, and therefore the electric charge charging capability of a variable electric power supply with respect to the load of the entire panel is exceeded.

[0183] The voltage required by the entire panel thus cannot be applied, and a sufficient panel display cannot be performed.

[0184] In embodiment 2, the sudden increase in electric current between the write-in period and the display period can be prevented by always leaving the switch of the electric power supply (reference numeral 709 of FIG. 7) turned on.

[0185] However, display is performed during the write-in period as well when using this method, and when the display period is shorter than the write-in period, such as in the write-in 4, the write-in 5, and the write-in 6 in FIG. 4C, it effectively becomes impossible to implement the display 4, the display 5, and the display 6.

[0186] In other words, when implementing embodiment 2, it is considered that the following points are necessary: 1) the number of pixels is reduced and the write-in period is shortened; 2) the performance of the TFTs contained in the driver circuits is increased and the operation speed is increased; and 3) using a structure in which the driver circuits are attached external to the panel, increasing the operating speed.

[0187] Embodiment 3

[0188] An embodiment of the present invention will be described referring to FIGS. 17 to 20. A method of simultaneously manufacturing TFTs of a pixel portion and a driver circuit portion provided in the periphery of the pixel portion will be described herein. Concerning the driver circuit, a CMOS circuit that is a base unit is shown in the figure, for a brief description.

[0189] First, a substrate 501 in which a base film (not shown) is disposed on the surface thereof is prepared as shown in FIG. 17(A). In this embodiment, a silicon nitride oxide film having a thickness of 100 nm and another silicon nitride oxide film having a thickness of 200 nm are laminated as a base film on a crystallized glass. At this time, preferably, the concentration of nitrogen of the film contacting the crystallized glass substrate is kept to 10-25 wt %. It is possible to form an element directly on the quartz substrate without forming any base film, of course.

[0190] Thereafter, an amorphous silicon film 502 whose thickness is 45 nm is formed on the substrate 501 by a well-known film formation method. There is no need to limit it to the amorphous silicon film. Instead, a semiconductor film (including a micro-crystal semiconductor film) that has an amorphous structure can be used in this embodiment. A compound semiconductor film that has an amorphous structure, such as an amorphous silicon germanium film, also can be used herein.

[0191] Concerning the steps from here to FIG. 17(C), it is possible to completely cite Japanese Laid-open Patent Publication No. 10-247735 filed by the present applicant. This publication discloses a technique concerning a method of crystallizing a semiconductor film, which uses an element, such as Ni, as a catalyst.

[0192] First, a protecting film 504 that has openings 503a and 503b is formed. A silicon oxide film having 150 nm

thick is used in this embodiment. A layer **505** that contains nickel (Ni containing layer) is formed on the protecting film **504** by a spin coating method.

[0193] Concerning the formation of the Ni containing layer, reference can be made to the above publication.